# LÓGICA DIGITAL Examen de la tercera evaluación

### Problema 1 (1'5p)

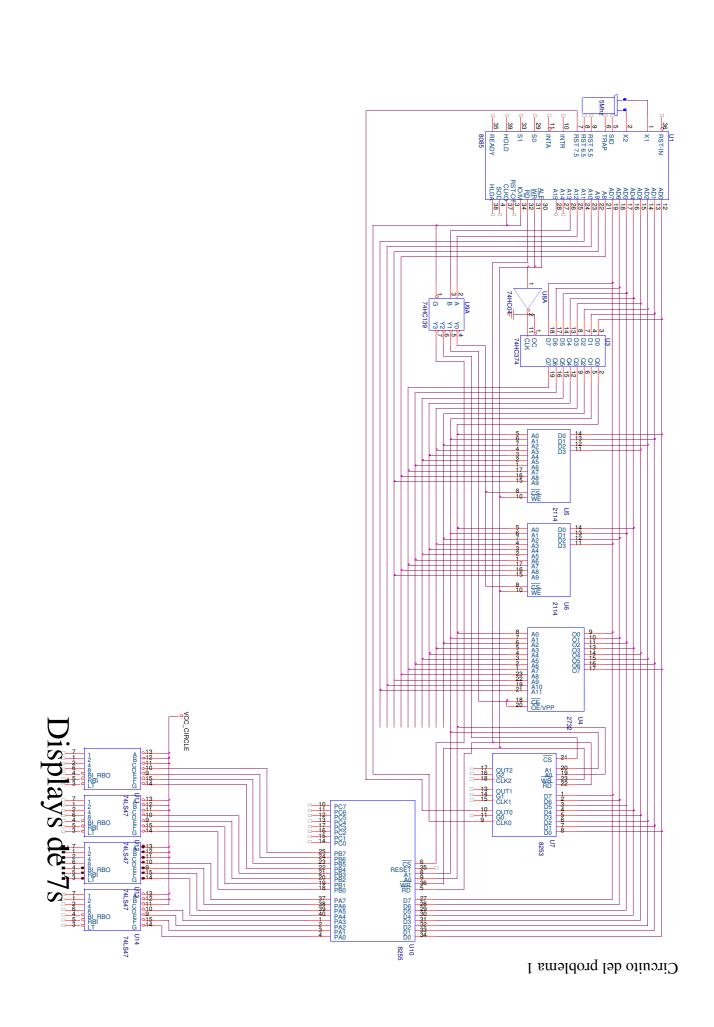

El circuito de la figura es un reloj digital basado en 8085.

Especificar si cada uno de los dispositivos está situado en memoria o en E/S y dibujar el mapa de memoria y el de E/S

#### **Problema 2 (1,5p)**

El siguiente código corresponde a un programa en ensamblador 8085.

ORG 3000H

Antes de ejecutar el programa los contenidos de la memoria y de los registros del micro son los siguientes (todo en hexadecimal).

LDA 3100H

1. Describir que hace el programa.

LXI H,3101H

2. ¿Cómo quedará la memoria y los registros después de la ejecución del programa?

ADD M

INX H

ADD M

INX H

ADD M

INX H

ADD M

STA 3105H

**HLT**

| Posición<br>de<br>memoria | contenido | regis<br>tro | contenido |

|---------------------------|-----------|--------------|-----------|

| 30FA                      | 21        | A            | 0         |

| 30FB                      | 10        | В            | 0         |

| 30FC                      | 12        | C            | 0         |

| 30FD                      | 0         | С            | 0         |

| 30FE                      | 0         | D            | 0         |

| 30FF                      | 0         | Е            | 0         |

| 3100                      | 12        | Н            | 0         |

| 3101                      | 45        |              |           |

| 3102                      | 65        | L            | 0         |

| 3103                      | 12        | esta         |           |

| 3104                      | 45        | do           | 0         |

| 3105                      | 1         | PC           | 3000      |

| 3106                      | 12        | CD           |           |

| 3107                      | 0         | SP           | 5000      |

| 3108                      | 0         |              |           |

| Posición<br>de<br>memoria | contenido |

|---------------------------|-----------|

| 30FA                      |           |

| 30FB                      |           |

| 30FC                      |           |

| 30FD                      |           |

| 30FE                      |           |

| 30FF                      |           |

| 3100                      |           |

| 3101                      |           |

| 3102                      |           |

| 3103                      |           |

| 3104                      |           |

| 3105                      |           |

| 3106                      |           |

| 3107                      |           |

| 3108                      |           |

| 3109                      |           |

| regis<br>tro | contenido |

|--------------|-----------|

| A            |           |

| В            |           |

| C            |           |

| D            |           |

| Е            |           |

| Н            |           |

| L            |           |

| esta<br>do   |           |

| PC           |           |

| SP           |           |

### Problema 3 (3'5p)

3109

Una central que suministra energía eléctrica dispone de 4 generadores, cada uno de los cuales puede

producir una potencia máxima de 200KW (pudiendo llegar a entregar una potencia máxima de 800KW entre todos). El funcionamiento de la central es el siguiente:

- El primer generador estará siempre funcionando, por pequeño que sea el consumo demandado, el segundo generador entra a funcionar cuando el consumo llega a 200KW, el tercero cuando llega a 400KW y el cuarto cuando llega a 600KW.

- Se ha dado cierta histéresis en la desconexión de los generadores de forma que el cuarto generador se desconecta cuando el consumo baja de los 500Kw, el tercero cuando lo hace por debajo de los 300KW y el segundo por debajo de los 100KW.

- En todo momento la central recibe información sobre la potencia demandada codificado en binario con tres bits de la siguiente forma:

| A B C | CONSUMO(KW)                           |  |

|-------|---------------------------------------|--|

| 000   | 0 <consumo<100< td=""></consumo<100<> |  |

| 001   | 100≤consumo<200                       |  |

| 010   | 200\(\leq\consumo\leq300\)            |  |

| 011   | 300\(\leq\consumo<\)400               |  |

| 100   | 400\(\leq\consumo<\footnote{500}      |  |

| 101   | 500\(\leq\consumo\)<600               |  |

| 110   | 600\(\leq\consumo\)<700               |  |

| 111   | 700\(\leq\consumo\)<800               |  |

• Los incrementos en la demanda siempre se producen en saltos pequeños, de como máximo 100KW en un segundo.

Se desea diseñar un autómata de Moore que controle la central a través de 4 señales G3, G2, G1, G0, activas a nivel alta, que indiquen cuando va a estar activo cada uno de los cuatro generadores.

- a) Realizar el diagrama de estados, explicando claramente su funcionamiento.

- b) Realizar el circuito a partir de biestables tipo D.

## **Problema 4 (3' 5p)**

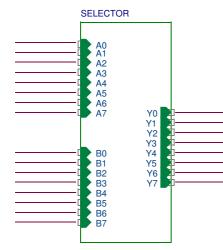

El circuito de la figura es un selector de datos que funciona de la siguiente forma:

A, B e Y son números binarios de 8 bits en binario puro sin signo.

El circuito saca por Y el mayor de los dos números A y B

Diseñar el ciruito a partir de dispositivos integrados para que se comporte según se pide. Explicar detalladamente el diseño del circuito, y cual es la función de cada uno de los dispositivos utilizados

## Problema 5(3' 5p)

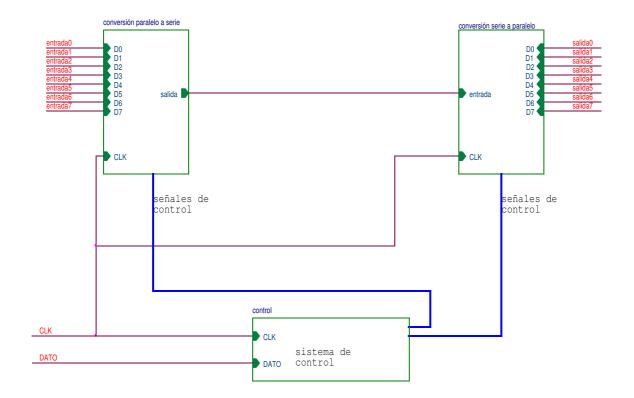

Se quiere diseñar un sistema para enviar datos de 8 bits a través de una línea serie, según el siguiente diagrama de bloques:

En el, el bloque de la izquierda carga el dato de 8 bits y lo convierte a série, transmitiéndolo en 8 pulsos de reloj por la línea serie. El bloque de la derecha recibe en 8 pulsos de reloj el dato por la línea serie y lo convierte a paralelo sacándolo por las lineas salida7..salida0. El sistema de control genera las señales necesarias para que los dos bloque funcionen correctamente.

La señal DATO, será un pulso a nivel bajo cuando haya un dato disponible en la entrada (entrada7..entrada0), y será la señal que marque el inicio del envío del dato, que durará 8 pulsos de reloj, quedando disponible en las salidas hasta que se envie un nuevo dato.

Para realizar el circuito se vana utilizar los componentes que aparecen en el esquema de la página siguiente, usando para los conversores 74LS194, y para el control un 74LS161 y las puertas lógicas que se crea necesario.

Completar el esquema del circuito, justificando claramente las conexiones que se hagan y la función de cada uno de los dispositivos.

salida7 salida6 salida5 salida4 salida3 salida2 salida1 salida0

| entrada7 entrada6 entrada5 entrada4 entrada3 entrada2 entrada1 entrada1 | 11 CL D QD 12 C D QD 13 A A ST QB SL SO QA 15 S1 |                | 11 CLIO 12 CLIO 12 CLIO 13 A A A A SR QB SI 14 SL SO QA SI U1                                                                           |

|-------------------------------------------------------------------------|--------------------------------------------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------|

|                                                                         | 74LS194A  74LS194A  11                           | serie          | 74LS194A<br>11 CIRC 12<br>5 D QD 12<br>6 C R QB 13<br>8 QC 13<br>8 QC 13<br>8 QC 14<br>9 SR QB 14<br>9 SL QA 15<br>10 S1 U3<br>74LS194A |

|                                                                         |                                                  | U5<br>74LS161A |                                                                                                                                         |

CLK DATO