**Radiation Hardened**

8-Bit CMOS Microprocessor

#### February 1996

### Features

- Devices QML Qualified in Accordance With MIL-PRF-38535

- Detailed Electrical and Screening Requirements are Contained in SMD# 5962-95824 and Harris' QM Plan

- Radiation Hardened EPI-CMOS

- Parametrics Guaranteed 1 x 10<sup>5</sup> RAD(Si)

- Transient Upset > 1 x 10<sup>8</sup> RAD(Si)/s

- Latch-up Free > 1 x  $10^{12}$  RAD(Si)/s

- Low Standby Current 500µA Max

- Low Operating Current 5.0mA/MHz (X<sub>1</sub> Input)

- Electrically Equivalent to Sandia SA 3000

- 100% Software Compatible with INTEL 8085

- Operation from DC to 2MHz, Post Radiation

- Single 5 Volt Power Supply

- On-Chip Clock Generator and System Controller

- Four Vectored Interrupt Inputs

- Completely Static Design

- Self Aligned Junction Isolated (SAJI) Process

- Military Temperature Range -55°C to +125°C

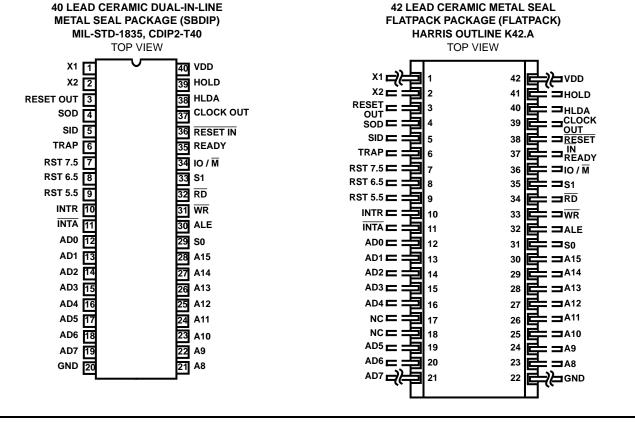

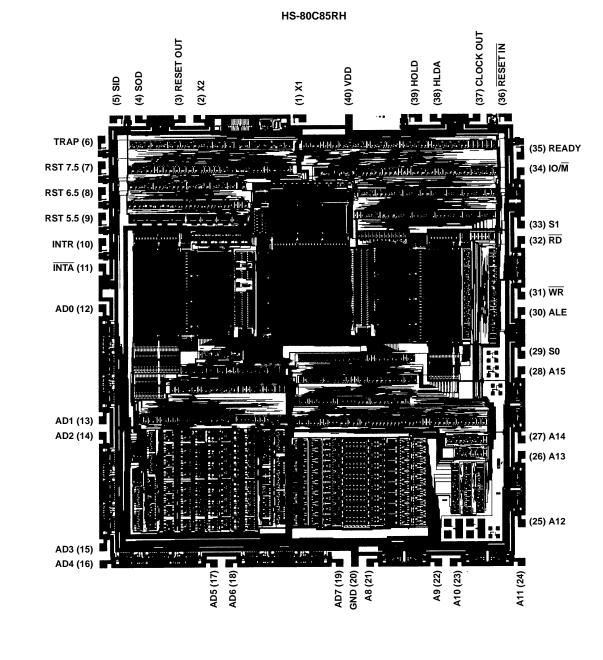

#### **Pinouts**

## Description

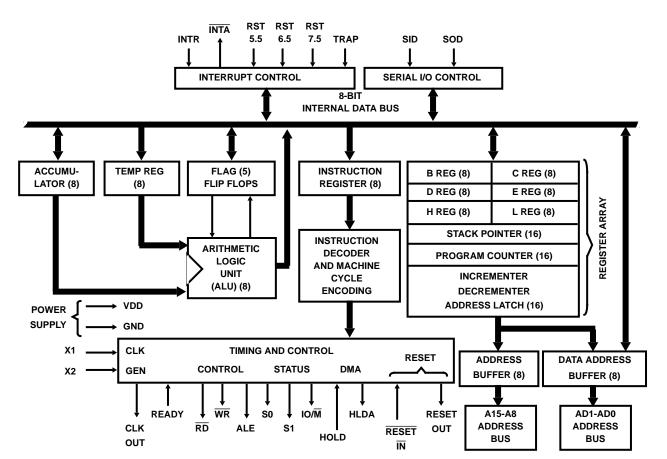

The HS-80C85RH is an 8-bit CMOS microprocessor fabricated using the Harris radiation hardened self-aligned junction isolated (SAJI) silicon gate technology. Latch-up free operation is achieved by the use of epitaxial starting material to eliminate the parasitic SCR effect seen in conventional bulk CMOS devices.

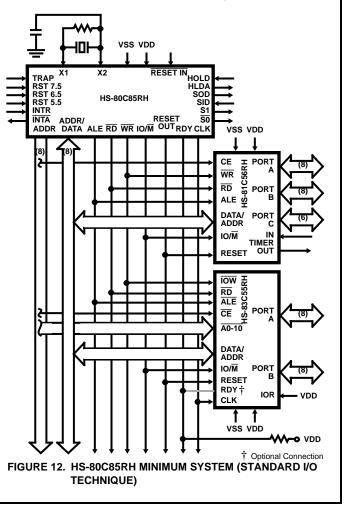

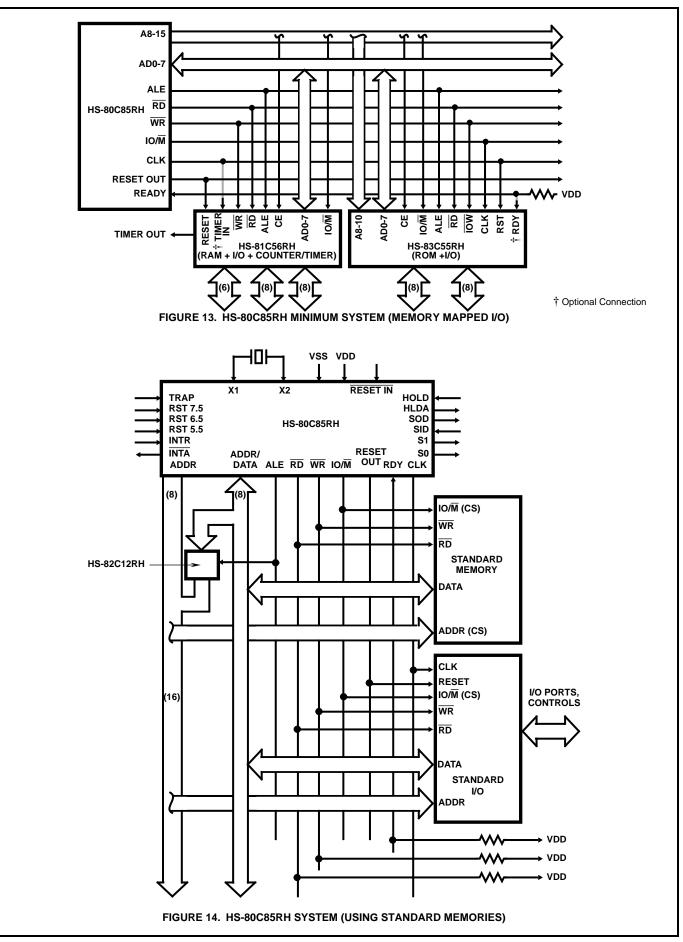

The HS-80C85RH is a functional logic emulation of the HMOS 8085 and its instruction set is 100% software compatible with the HMOS device. The HS80C85RH is designed for operation with a single 5 volt power supply. Its high level of integration allows the construction of a radiation hardened microcomputer system with as few as three ICs (HS-80C85RH CPU, HS83C55RH ROM I/O, and the HS-81C55/56RH RAM I/O.

CAUTION: These devices are sensitive to electrostatic discharge. Users should follow proper IC Handling Procedures. Copyright © Harris Corporation 1996

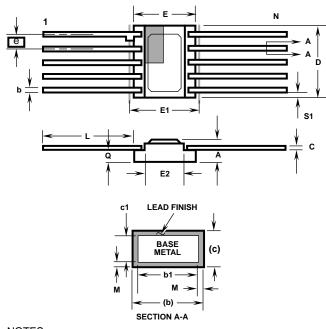

#### **Ordering Information** PART NUMBER **TEMPERATURE RANGE** SCREENING LEVEL PACKAGE -55°C to +125°C MIL-PRF-38535 Level Q 40 Lead SBDIP 5962R9582401QQC 5962R9582401QXC -55°C to +125°C MIL-PRF-38535 Level Q 42 Lead Ceramic Flatpack 5962R9582401VQC MIL-PRF-38535 Level V 40 Lead SBDIP -55°C to +125°C 5962R9582401VXC -55°C to +125°C MIL-PRF-38535 Level V 42 Lead Ceramic Flatpack +25°C 40 Lead SBDIP HS1-80C85RH/SAMPLE Sample +25°C HS9-80C85RH/SAMPLE Sample 42 Lead Ceramic Flatpack

# **Functional Diagram**

# Pin Description

| SYMBOL      | PIN<br>NUMBER | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                              |

|-------------|---------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A8 - A15    | 21-28         | 0    | Address Bus: The most significant 8 bits of the memory address or the 8 bits of the I/O address 3-stated during Hold and Halt modes and during RESET.                                                                                                                                                                                                                                                                    |

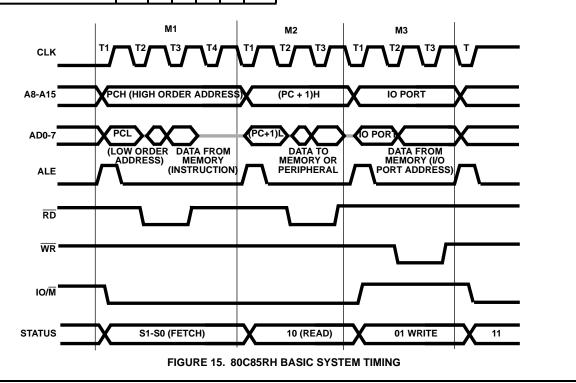

| AD0-7       | 12-19         | I/O  | Multiplexed Address/Data Bus: Lower 8 bits of the memory address (or I/O address) appear of the bus during the first clock cycle (T state) of a machine cycle. It then becomes the data bus during the second and third clock cycles.                                                                                                                                                                                    |

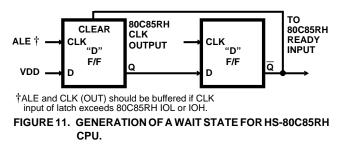

| ALE         | 32            | 0    | Address Latch Enable: It occurs during the first clock state of a machine cycle and enables th address to get latched into the on-chip latch of peripherals. The falling edge of ALE is set to gua antee setup and hold times for the address information. The falling edge of ALE can also be use to strobe the status information. ALE is never 3-stated.                                                              |

| S0, S1, and | 31, 35,       | 0    | Machine Cycle Status:                                                                                                                                                                                                                                                                                                                                                                                                    |

| IO/M        | & 36          |      | IO/M S1 S0 Status                                                                                                                                                                                                                                                                                                                                                                                                        |

|             |               |      | 0 0 1 Memory write                                                                                                                                                                                                                                                                                                                                                                                                       |

|             |               |      | 0 1 0 Memory write                                                                                                                                                                                                                                                                                                                                                                                                       |

|             |               |      | 1 0 1 I/O write                                                                                                                                                                                                                                                                                                                                                                                                          |

|             |               |      | 1 1 0 I/O read                                                                                                                                                                                                                                                                                                                                                                                                           |

|             |               |      | 0 1 1 Opcode fetch                                                                                                                                                                                                                                                                                                                                                                                                       |

|             |               |      | 1 1 0pcode fetch                                                                                                                                                                                                                                                                                                                                                                                                         |

|             |               |      | 1 1 Interrupt acknowledge                                                                                                                                                                                                                                                                                                                                                                                                |

|             |               |      | T 0 0 Halt                                                                                                                                                                                                                                                                                                                                                                                                               |

|             |               |      | T X X Hold                                                                                                                                                                                                                                                                                                                                                                                                               |

|             |               |      | T X X Reset                                                                                                                                                                                                                                                                                                                                                                                                              |

|             |               |      | T = 3-State (high impedance)<br>X = Unspecified                                                                                                                                                                                                                                                                                                                                                                          |

|             |               |      | S1 can be used as an advanced $R/\overline{W}$ status. IO/ $\overline{M}$ , S0 and S1 become valid at the beginning of a machine cycle and remain stable throughout the cycle. The falling edge of ALE may be use to latch the state of these lines.                                                                                                                                                                     |

| RD          | 34            | 0    | Read Control: A low level on RD indicates the selected memory or I/O device is to be read ar that the Data Bus is available for the data transfer, 3-stated during Hold and Halt modes and during RESET.                                                                                                                                                                                                                 |

| WR          | 33            | 0    | Write Control: A low level on $\overline{WR}$ indicates the data on the Data Bus is to be written into the s lected memory or I/O location. Data is set up at the trailing edge of $\overline{WR}$ , 3-stated during Hold an Halt modes and during RESET.                                                                                                                                                                |

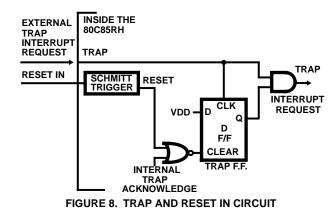

| READY       | 35            | Ι    | Ready: If READY is high during a read or write cycle, it indicates that the memory or peripher is ready to send or receive data. If READY is low, the cpu will wait an integral number of cloc cycles for READY to go high before completing the read or write cycle. READY must conform specified setup and hold times.                                                                                                 |

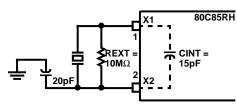

| HOLD        | 39            | I    | Hold: Indicates that another master is requesting the use of the address and data buses. The cpu, upon receiving the hold request, will relinquish the use of the bus as soon as the completion of the current bus transfer. Internal processing can continue. The processor can regain the bus only after the HOLD is removed. When the HOLD is acknowledged, the Address, Data Bus, RIWR, and IO/M lines are 3-stated. |

| HLDA        | 38            | 0    | Hold Acknowledge: Indicates that the cpu has received the HOLD request and that it will relia<br>quish the bus in the next clock cycle. HLDA goes low after the Hold request is removed. The cp<br>takes the bus one half clock cycle after HLDA goes low.                                                                                                                                                               |

**Pin Description** (Continued)

| SYMBOL                        | PIN<br>NUMBER | TYPE   | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-------------------------------|---------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INTR                          | 10            | I      | Interrupt Request: Is used as a general purpose interrupt. It is sampled only during the next to the last clock cycle of an instruction and during Hold and Halt states. If it is active, the Program Counter (PC) will be inhibited from incrementing and an INTA will be issued. During this cycle a RESTART or CALL instruction can be inserted to jump to the interrupt service routine. The INTR is enabled and disabled by software. It is disabled by Reset and immediately after an interrupt is accepted.                                                                                                                                                                                                                                       |

| INTA                          | 11            | 0      | Interrupt Acknowledge: Is used instead of (and has the same timing as) $\overline{RD}$ during the Instruction cycle after an INTR is accepted. It can be used to activate an 8259A Interrupt chip or some other interrupt port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| RST 5.5<br>RST 6.5<br>RST 7.5 | 9<br>8<br>7   | I      | Restart Interrupts: These three inputs have the same timing as INTR except they cause an internal RESTART to be automatically inserted.<br>The priority of these interrupts is ordered as shown in Table 6. These interrupts have a higher priority than INTR. In addition, they may be individually masked out using the SIM instruction.                                                                                                                                                                                                                                                                                                                                                                                                               |

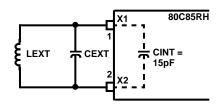

| TRAP                          | 6             | I      | Trap: Trap interrupt is a non-maskable RESTART interrupt. It is recognized at the same time as INTR or RST 5.5-7.5. It is unaffected by any mask or Interrupt Enable. It has the highest priority of any interrupt. (See Table 6.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

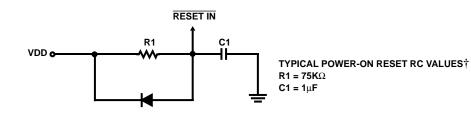

| RESET IN                      | 36            | I      | Reset In: Sets the Program Counter to zero and resets the Interrupt Enable and HLDA flip-flops. The data and address buses and the control lines are 3-stated during RESET and because of the asynchronous nature of RESET the processor's internal registers and flags may be altered by RESET with unpredictable results. RESET IN is a Schmitt-triggered input, allowing connection to an R-C network for power-on RESET delay (see Figure 1). Upon power-up, RESET IN must remain low for at least 10 "clock cycle" after minimum VDD has been reached. For proper reset operation after the power-up duration, RESET IN should be kept low a minimum of three clock periods. The CPU is held in the reset condition as long as RESET IN is applied. |

| RESET OUT                     | 3             | 0      | Reset Out: Reset Out indicates cpu is being reset. Can be used as a system reset. The signal is synchronized to the processor clock and lasts an integral number of clock periods.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

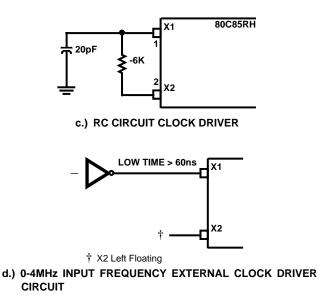

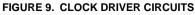

| X1<br>X2                      | 1<br>2        | l<br>O | X1 and X2: Are connected to a crystal, LC, or RC network to drive the internal clock generator. X, can also be an external clock Input from a logic gate. The input frequency is divided by 2 to give the processor's internal operating frequency.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

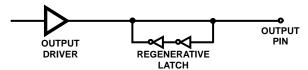

| CLK                           | 37            | 0      | Clock: Clock output for use as a system clock. The period of CLK is twice the X1, X2 input period.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| SID                           | 5             | I      | Serial Input Data Line: The data on this line is loaded into accumulator bit 7 whenever a RIM instruction is executed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| SOD                           | 4             | 0      | Serial Output Data Line: The output SOD is set or reset as specified by the SIM instruction.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| VCC                           | 40            | I      | Power: +5V supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| GND                           | 20            | I      | Ground: Reference.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

$\ensuremath{^\dagger}$  Values may have to vary due to applied power supply ramp up time.

FIGURE 1. POWER-ON RESET CIRCUIT

#### **Absolute Maximum Ratings**

| Supply Voltage+7.0V                                |

|----------------------------------------------------|

| Input, Output or I/O Voltage GND-0.3V to VCC+0.3V  |

| Storage Temperature Range65°C to +150°C            |

| Junction Temperature                               |

| Lead Temperature (Soldering 10s)                   |

| Typical Derating Factor2.0mA/MHz Increase in IDDOP |

| ESD Classification Class 1                         |

#### **Reliability Information**

| Thermal Resistance<br>SBDIP Package<br>Ceramic Flatpack Package | θ <sub>JA</sub><br>45°C/W<br>77°C/W | θ <sub>JC</sub><br>10ºC/W<br>13ºC/W |

|-----------------------------------------------------------------|-------------------------------------|-------------------------------------|

| Maximum Package Power Dissipation at +125                       | 5°C Ambien                          | t                                   |

| SBDIP Package                                                   |                                     |                                     |

| Ceramic Flatpack Package                                        |                                     | 0.65W                               |

| If device power exceeds package dissipation of                  | capability, p                       | rovide heat                         |

| sinking or derate linearly at the following rate:               |                                     |                                     |

| SBDIP Package                                                   | 2                                   | 22.2mW/ºC                           |

| Ceramic Flatpack Package                                        | 1                                   | 3.0mW/ <sup>o</sup> C               |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### **Operating Conditions**

|                                      |               |                                                                               | GROUP A   |                                                                   | LIM      | ITS |        |

|--------------------------------------|---------------|-------------------------------------------------------------------------------|-----------|-------------------------------------------------------------------|----------|-----|--------|

| PARAMETER                            | SYMBOL        | CONDITIONS                                                                    | SUBGROUPS | TEMPERATURE                                                       | MIN      | MAX | UNITS  |

| Input Leakage<br>Current             | IIH or<br>IIL | VDD = 5.25V, VI = VDD<br>or GND                                               | 1, 2, 3   | -55 <sup>o</sup> C, +25 <sup>o</sup> C, or<br>+125 <sup>o</sup> C | -1.0     | 1.0 | μA     |

| High Level Output<br>Voltage         | VOH           | VDD = 4.75V, IOH = -1.0mA                                                     | 1, 2, 3   | -55°C, +25°C, or<br>+125°C                                        | VDD -0.5 | -   | V      |

| Low Level Output<br>Voltage          | VOL           | VDD = 5.25V, IOL = 1.0mA,                                                     | 1, 2, 3   | -55°C, +25°C, or<br>+125°C                                        | -        | 0.5 | V      |

| Static Current                       | IDDSB         | VDD = 5.25V, Clock Out = Hi<br>and Low                                        | 1, 2, 3   | -55°C, +25°C, or<br>+125°C                                        | -        | 500 | μA     |

| Operating Supply<br>Current (Note 2) | IDDOP         | VDD = 5.25V, f = 1MHz<br>(Note 2)                                             | 1, 2, 3   | -55°C, +25°C, or<br>+125°C                                        | -        | 5.0 | mA/MHz |

| Functional Tests                     | FT            | VDD = 4.75V and 5.25V,<br>TCYC = 500ns,<br>VOL $\leq$ VDD/2, VOH $\geq$ VDD/2 | 7, 8A, 8B | -55°C, +25°C, or<br>+125°C                                        | -        | -   | -      |

#### NOTES:

1. All devices guaranteed at worst case limits and over radiation.

2. Operating supply current (IDDOP) is proportional to crystal frequency. Parts are tested at 1MHz

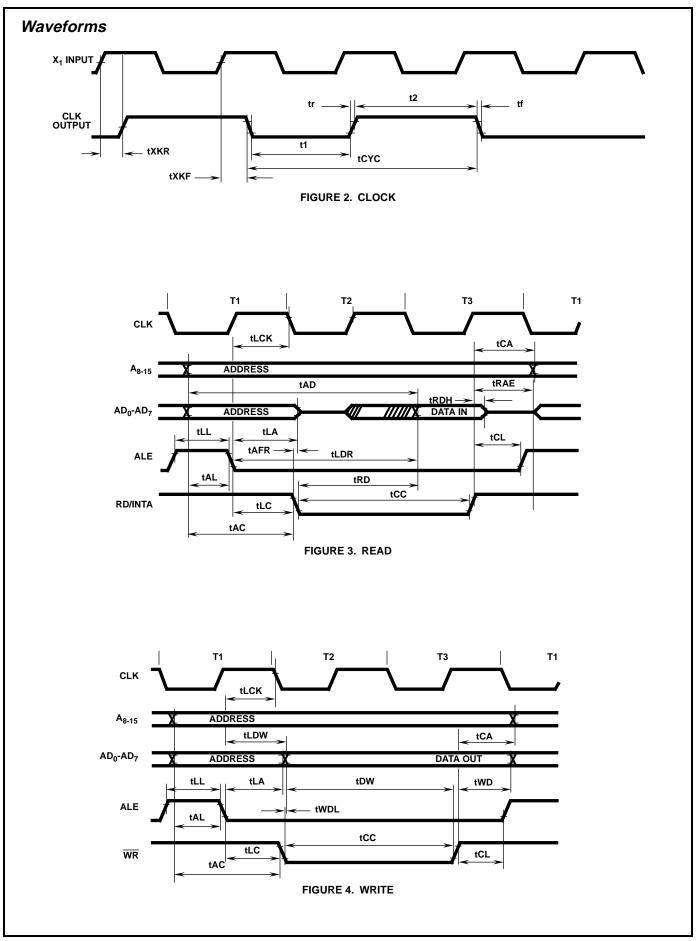

#### TABLE 2. AC ELECTRICAL PERFORMANCE CHARACTERISTICS

|                                                 |        | GROUP A   |                      | LIN | IITS |       |

|-------------------------------------------------|--------|-----------|----------------------|-----|------|-------|

| PARAMETER                                       | SYMBOL | SUBGROUPS | TEMPERATURE          | MIN | MAX  | UNITS |

| CLK Low Time (Standard CLK Loading)             | T1     | 9, 10, 11 | -55°C, +25°C, +125°C | 40  | -    | ns    |

| CLK High Time (Standard CLK Loading)            | T2     | 9, 10, 11 | -55°C, +25°C, +125°C | 100 | -    | ns    |

| CLK Rise Time                                   | Tr     | 9, 10, 11 | -55°C, +25°C, +125°C | -   | 115  | ns    |

| CLK Fall Time                                   | Tf     | 9, 10, 11 | -55°C, +25°C, +125°C | -   | 115  | ns    |

| X1 Rising to CLK Rising                         | TXKR   | 9, 10, 11 | -55°C, +25°C, +125°C | 30  | 250  | ns    |

| X1 Rising to CLK Falling                        | TXKF   | 9, 10, 11 | -55°C, +25°C, +125°C | 50  | 275  | ns    |

| A8-15 Valid to Leading Edge of Control (Note 5) | TAC    | 9, 10, 11 | -55°C, +25°C, +125°C | 300 | -    | ns    |

| A0-7 Valid to Leading Edge of Control           | TACL   | 9, 10, 11 | -55°C, +25°C, +125°C | 300 | -    | ns    |

| A0-15 Valid to Valid Data In                    | TAD    | 9, 10, 11 | -55°C, +25°C, +125°C | 875 | -    | ns    |

| Address Float After Leading Edge of READ (INTA) | TAFR   | 9, 10, 11 | -55°C, +25°C, +125°C | -   | 70   | ns    |

|                                                          |        | GROUP A   |                      | LIN |     |       |

|----------------------------------------------------------|--------|-----------|----------------------|-----|-----|-------|

| PARAMETER                                                | SYMBOL | SUBGROUPS | TEMPERATURE          | MIN | MAX | UNITS |

| A8-15 Valid Before Trailing Edge of ALE (Note 5)         | TAL    | 9, 10, 11 | -55°C, +25°C, +125°C | 75  | -   | ns    |

| A0-7 Valid Before Trailing Edge of ALE                   | tALL   | 9, 10, 11 | -55°C, +25°C, +125°C | 125 | -   | ns    |

| READY Valid from Address<br>Valid                        | TARY   | 9, 10, 11 | -55°C, +25°C, +125°C | 250 | -   | ns    |

| Address (A8-15) Valid After Control                      | TCA    | 9, 10, 11 | -55°C, +25°C, +125°C | 150 | -   | ns    |

| Width of Control Low (RD, WR, INTA) Edge of ALE          | TCC    | 9, 10, 11 | -55°C, +25°C, +125°C | 575 | -   | ns    |

| Trailing Edge of Control to Leading Edge of ALE          | TCL    | 9, 10, 11 | -55°C, +25°C, +125°C | 60  | -   | ns    |

| Data Valid to Trailing Edge of WRITE                     | TDW    | 9, 10, 11 | -55°C, +25°C, +125°C | 575 | -   | ns    |

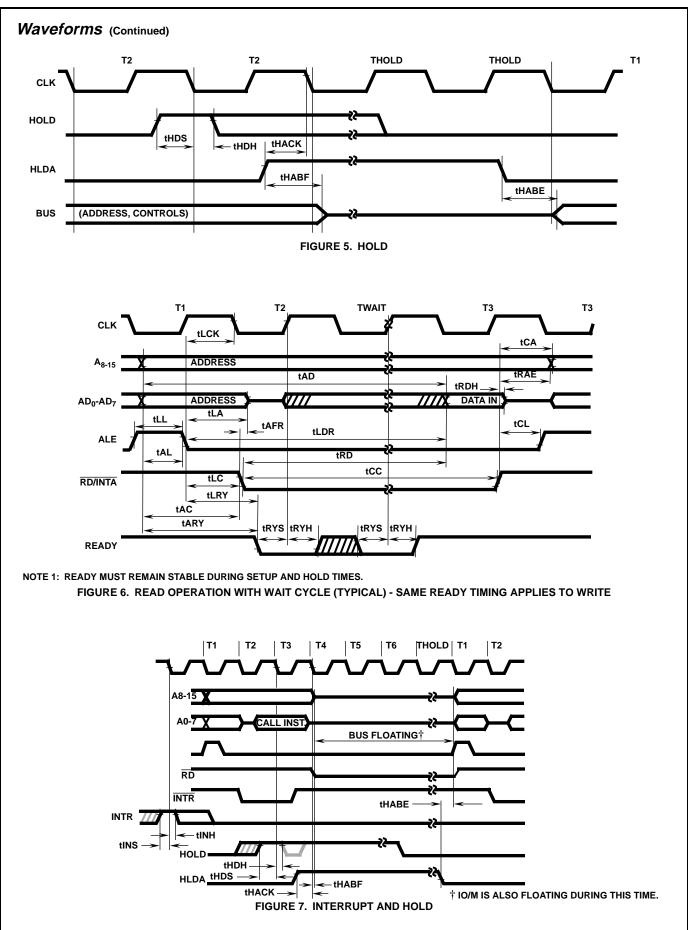

| HLDA to Bus Enable                                       | THABE  | 9, 10, 11 | -55°C, +25°C, +125°C | -   | 375 | ns    |

| Bus Float After HLDA                                     | THABF  | 9, 10, 11 | -55°C, +25°C, +125°C | -   | 375 | ns    |

| HLDA Valid to Trailing Edge of CLK                       | THACK  | 9, 10, 11 | -55°C, +25°C, +125°C | 90  | -   | ns    |

| HOLD Hold Time                                           | THDH   | 9, 10, 11 | -55°C, +25°C, +125°C | -   | 0   | ns    |

| HOLD Setup Time to Trailing Edge of CLK                  | THDS   | 9, 10, 11 | -55°C, +25°C, +125°C | -   | 300 | ns    |

| INTR Hold Time                                           | TINH   | 9, 10, 11 | -55°C, +25°C, +125°C | -   | 0   | ns    |

| INTR, RST and TRAP Setup Time to Falling<br>Edge of CLK  | TINS   | 9, 10, 11 | -55°C, +25°C, +125°C | -   | 375 | ns    |

| Address Hold Time After ALE                              | TLA    | 9, 10, 11 | -55°C, +25°C, +125°C | 75  | -   | ns    |

| Trailing Edge of ALE to Leading Edge of Control          | TLC    | 9, 10, 11 | -55°C, +25°C, +125°C | 150 | -   | ns    |

| ALE Low During CLK High                                  | TLCK   | 9, 10, 11 | -55°C, +25°C, +125°C | 125 | -   | ns    |

| ALE to Valid Data During Read                            | TLDR   | 9, 10, 11 | -55°C, +25°C, +125°C | 675 | -   | ns    |

| ALE to Valid Data During Write                           | TLDW   | 9, 10, 11 | -55°C, +25°C, +125°C | -   | 350 | ns    |

| ALE Width                                                | TLL    | 9, 10, 11 | -55°C, +25°C, +125°C | 200 | -   | ns    |

| ALE to READY Stable                                      | TLRY   | 9, 10, 11 | -55°C, +25°C, +125°C | -   | 175 | ns    |

| Trailing Edge of READ to Re-Enabling the Ad-<br>dress    | TRAE   | 9, 10, 11 | -55°C, +25°C, +125°C | 120 | -   | ns    |

| READ (or INTA) to Valid Data                             | TRD    | 9, 10, 11 | -55°C, +25°C, +125°C | 375 | -   | ns    |

| Control Trailing Edge to Leading Edge of Next<br>Control | TRV    | 9, 10, 11 | -55°C, +25°C, +125°C | 550 | -   | ns    |

| Data Hold Time After READ INTA                           | TRDH   | 9, 10, 11 | -55°C, +25°C, +125°C | -   | 0   | ns    |

| READY Hold Time                                          | TRYH   | 9, 10, 11 | -55°C, +25°C, +125°C | -   | 0   | ns    |

| READY Setup Time to Leading Edge of CLK                  | TRYS   | 9, 10, 11 | -55°C, +25°C, +125°C | 250 | -   | ns    |

| Data Valid After Trailing Edge of WRITE                  | TWD    | 9, 10, 11 | -55°C, +25°C, +125°C | 150 | -   | ns    |

| LEADING Edge of WRITE to Data Valid                      | TWDL   | 9, 10, 11 | -55°C, +25°C, +125°C | -   | 50  | ns    |

#### TABLE 2. AC ELECTRICAL PERFORMANCE CHARACTERISTICS (Continued)

NOTES:

1. Output timings are measured with a purely capacitive load, CL = 150pF

2. VDD = 4.75V, VIH = 4.25V, VIL = 0.8V

3. Delay times are measured with a 1MHz clock. An algorithm is used to convert the delays into the AC timings above with a TCYC = 500ns.

4. The AC table is tested as shown above to guarantee the processor system timing.

5. A8 - A15 address specifications also apply to IO/M, S0 and S1 except A8 - A15 are undefined during T4-T6 of off cycle whereas IO/M, So, and S1 are stable.

#### TABLE 3. ELECTRICAL PERFORMANCE CHARACTERISTICS

|                    | (NOTE 1) |                      |                      | LIMITS |     |       |  |

|--------------------|----------|----------------------|----------------------|--------|-----|-------|--|

| PARAMETER          | SYMBOL   | CONDITIONS           | TEMPERATURE          | MIN    | MAX | UNITS |  |

| Input Capacitance  | CIN      | VDD = Open, f = 1MHz | $T_A = +25^{\circ}C$ | -      | 12  | pF    |  |

| I/O Capacitance    | CI/O     | VDD = Open, f = 1MHz | $T_A = +25^{\circ}C$ | -      | 13  | pF    |  |

| Output Capacitance | COUT     | VDD = Open, f = 1MHz | $T_A = +25^{\circ}C$ | -      | 12  | pF    |  |

NOTE:

1. All measurements referenced to device ground.

#### TABLE 4. POST 100K RAD ELECTRICAL PERFORMANCE CHARACTERISTICS

NOTE: The post irradiation test conditions and limits are the same as those listed in Tables 1 and 2.

TABLE 5. BURN-IN DELTA PARAMETERS (+25°C; In Accordance With SMD)

#### TABLE 6. INTERRUPT PRIORITY, RESTART ADDRESS, AND SENSITIVITY

| NAME    | PRIORITY | ADDRESS BRANCHED TO (1)<br>WHEN INTERRUPT OCCURS | TYPE TRIGGER                              |

|---------|----------|--------------------------------------------------|-------------------------------------------|

| TRAP    | 1        | 24H                                              | Rising edge and high level until sampled. |

| RST 7.5 | 2        | 3CH                                              | Rising edge (latched)                     |

| RST 6.5 | 3        | 34CH                                             | High level until sampled.                 |

| RST 5.5 | 4        | 2CH                                              | High level until sampled.                 |

| INTR    | 5        | See Note 2                                       | High level until sampled.                 |

NOTES:

1. The processor pushes the PC on the stack before branching to the indicated address.

2. The address branched to depends on the instruction provided to the cpu when the interrupt is acknowledged.

| TABLE 7. E | <b>BUS TIMING</b> | SPECIFICATION AS | A t <sub>CYC</sub> DEPENDENT |

|------------|-------------------|------------------|------------------------------|

|------------|-------------------|------------------|------------------------------|

| OL | HS-80C85RH       |         | SYMBOL | HS-80C85RH       |         |

|----|------------------|---------|--------|------------------|---------|

|    | (1/2)T- 175      | Minimum | tCC    | (3/2 + N)T - 175 | Minimun |

|    | (1/2)T- 175      | Minimum | tCL    | (1/2)T - 190     | Minimun |

|    | (1/2)T-50        | Minimum | tARY   | (3/2)T - 500     | Maximur |

| <  | (1/2)T- 125      | Minimum | tHACK  | (1/2)T - 160     | Minimun |

|    | (1/2)T- 100      | Minimum | tHABF  | (1/2)T +125      | Maximur |

| )  | (5/2 + N)T - 375 | Maximum | tHABE  | (1/2)T +125      | Maximur |

| )  | (3/2 + N)T - 375 | Maximum | tAC    | (2/2)T - 200     | Minimum |

| E  | (1/2)T- 130      | Minimum | t1     | (1/2)T-210       | Minimum |

| ۱. | (1/2)T - 100     | Minimum | t2     | (1/2)T- 150      | Minimum |

| /  | (3/2 + N)T - 175 | Minimum | tRV    | (3/2)T - 200     | Minimum |

| )  | (1/2)T-100       | Minimum | tLDR   | (4/2)T - 325     | Maximur |

NOTE: N is equal to the total WAIT states T = tCYC

HS-80C85RH

| IMMEMONIC         Do.         Do. <thdo.< th="">         Do.         <thdo.< th=""> <thdo.<< th=""><th></th><th colspan="6">INSTRUCTION CODE</th><th>E</th><th></th><th colspan="2">OPERATIONS</th><th colspan="7">INSTRUCTION CODE</th><th>OPERATIONS</th></thdo.<<></thdo.<></thdo.<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |            | INSTRUCTION CODE |                |       |                |          |                | E              |                | OPERATIONS          |            | INSTRUCTION CODE |                |       |       |       |                |                | OPERATIONS     |                                       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------------------|----------------|-------|----------------|----------|----------------|----------------|----------------|---------------------|------------|------------------|----------------|-------|-------|-------|----------------|----------------|----------------|---------------------------------------|

| MOV11, I2       0       1       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | MNEMONIC   | D <sub>7</sub>   | D <sub>6</sub> | $D_5$ | D <sub>4</sub> | $D_3$    | D <sub>2</sub> | D <sub>1</sub> | D <sub>0</sub> |                     | MNEMONIC   | D <sub>7</sub>   | D <sub>6</sub> | $D_5$ | $D_4$ | $D_3$ | D <sub>2</sub> | D <sub>1</sub> | D <sub>0</sub> |                                       |

| MOV         Main                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | MOVE, LOAD | , and            | D STO          | ORE   |                |          |                |                |                |                     | RNZ        | 1                | 1              | 0     | 0     | 0     | 0              | 0              | 0              | Return on no zero                     |

| MOV M.r         0         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1        1         1         1 <td>MOVr1, r2</td> <td>0</td> <td>1</td> <td>D</td> <td>D</td> <td>D</td> <td>S</td> <td>S</td> <td>S</td> <td>U U</td> <td>RP</td> <td>1</td> <td>1</td> <td>1</td> <td>1</td> <td>0</td> <td>0</td> <td>0</td> <td>0</td> <td>Return on positive</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | MOVr1, r2  | 0                | 1              | D     | D              | D        | S              | S              | S              | U U                 | RP         | 1                | 1              | 1     | 1     | 0     | 0              | 0              | 0              | Return on positive                    |

| MOV r.M     0     1     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0 <t< td=""><td></td><td>0</td><td></td><td></td><td></td><td></td><td><u> </u></td><td></td><td></td><td>- 5</td><td>RM</td><td>1</td><td>1</td><td>1</td><td>1</td><td>1</td><td>0</td><td>0</td><td>0</td><td>Return on minus</td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |            | 0                |                |       |                |          | <u> </u>       |                |                | - 5                 | RM         | 1                | 1              | 1     | 1     | 1     | 0              | 0              | 0              | Return on minus                       |

| MV1     0     0     D     D     1     1     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |            |                  |                |       |                |          |                |                |                | memory              | RPE        | 1                | 1              | 1     | 0     | 1     | 0              | 0              | 0              |                                       |

| MVI M         0         1         1         0         Move immediate memory         Rest ART           MVI M         0         0         1         1         0         Move immediate memory         Rest ART           LXI B         0         0         0         0         0         0         0         0         1         1         0         1         1         Nove immediate memory           LXI D         0         0         0         0         0         0         0         1         Load immediate megister Pair D & E         Nove immediate megister Pair D & E           LXI D         0         0         0         0         0         0         0         1         Load immediate megister Pair D & E           STAX D         0         0         0         0         0         0         0         0         1         0         1         0         1         0         1         0         1         0         0         1         0         0         0         0         1         1         0         1         0         0         1         1         0         1         0         1         0         0         1         0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |            |                  |                |       |                |          |                |                |                | register            | RPO        | 1                | 1              | 1     | 0     | 0     | 0              | 0              | 0              |                                       |

| MMM         0         0         1         0         Mode Mineralize<br>memory           LXI         0         0         0         0         0         0         0         1         Load Immediate<br>register Pair B & C           LXI         0         0         0         0         0         0         0         1         Load Immediate<br>register Pair B & C           LXI         0         0         0         0         0         0         0         0         0         0         1         1         Load Immediate<br>register Pair B & C           STAX         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | MVI r      | 0                | 0              | D     | D              | D        | 1              | 1              | 0              |                     | RESTART    |                  |                |       |       | 8     |                |                |                | •                                     |

| LXI B         0         0         0         0         0         0         0         0         1         Load immediate register Pair B & C           LXI D         0         0         0         1         0         1         1         Load immediate register Pair B & C           LXI D         0         0         1         0         1         0         1         0         1         0         1         1         0         1         1         0         1         1         0         1         1         0         1         1         0         1         1         0         1         1         0         1         1         0         1         1         0         1         1         0         1         1         0         1         1         0         1         1         0         1         1         0         1         1         0         1         1         0         1         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | MVI M      | 0                | 0              | 1     | 1              | 0        | 1              | 1              | 0              | Move immediate      | RST        | 1                | 1              | А     | А     | А     | 1              | 1              | 1              | Restart                               |

| Image: Normal Sector       Image: Normal Sector <th< td=""><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td>memory</td><td>INPUT/OUTP</td><td>UT</td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td>•</td></th<>                                                                                                                                                                                                                                                                                                             |            |                  |                |       |                |          |                |                |                | memory              | INPUT/OUTP | UT               |                |       |       |       |                |                |                | •                                     |

| LXID         0         0         1         0         1         0         1         1         0         1         0         0         1         1         0         0         1         1         0         0         1         0         0         1         1         0         1         0         0         0         1         1         1         0         1         0         0         0         1         1         0         1         0         0         0         1         1         0         1         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | LXI B      | 0                | 0              | 0     | 0              | 0        | 0              | 0              | 1              |                     | IN         | 1                | 1              | 0     | 1     | 1     | 0              | 1              | 1              | Input                                 |

| Image: Market | LXI D      | 0                | 0              | 0     | 1              | 0        | 0              | 0              | 1              | •                   | OUT        | 1                | 1              | 0     | 1     | 0     | 0              | 1              | 1              | Output                                |

| STAX B       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       1       0       0       0       0       1       0       1       0       0       0       0       0       0       1       0       1       0       1       0       1       0       1       0       1       0       1       0       1       0       1       0       1       0       1       0       1       0       1       0       1       0       1       0       1       0       1       0       1       0       1       0       1       0       1       0       1       0       0       1       0       1       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0 <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td>-</td> <td></td> <td></td> <td></td> <td>INCREMENT</td> <td>AND</td> <td>DEC</td> <td>REM</td> <td>ENT</td> <td></td> <td></td> <td></td> <td></td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |            |                  |                |       |                |          | -              |                |                |                     | INCREMENT  | AND              | DEC            | REM   | ENT   |       |                |                |                |                                       |

| STAX B         0         0         0         0         0         0         0         0         0         0         0         1         0         Store A indirect           STAX B         0         0         0         1         0         Store A indirect           LDAX B         0         0         0         1         0         0         1         0         Store A indirect           LDAX D         0         0         1         1         0         1         0         1         0         0         1         0         0         1         1         0         0         0         1         1         0         0         0         0         1         1         0         0         0         0         0         0         1         1         0         0         0         0         1         0         0         0         0         0         0         0         1         1         0         0         0         0         1         1         0         0         0         1         1         1         1         0         0         1         1         1         1         0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | LXI H      | 0                | 0              | 1     | 0              | 0        | 0              | 0              | 1              |                     | INR r      | 0                | 0              | D     | D     | D     | 1              | 0              | 0              | Increment register                    |

| STAX D         0         0         0         0         0         1         1         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         1         0         0         0         0         1         0         0         0         0         1         0         0         0         0         1         1         0         0         0         0         1         1         0         0         0         1         1         0         0         1         1         0         0         1         1         0         0         1         1         0         0         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1 <td>OTAY D</td> <td>0</td> <td>0</td> <td></td> <td></td> <td></td> <td>0</td> <td></td> <td>0</td> <td>, e</td> <td>DCR r</td> <td>0</td> <td>0</td> <td>D</td> <td>D</td> <td>D</td> <td>1</td> <td>0</td> <td>1</td> <td>Decrement register</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | OTAY D     | 0                | 0              |       |                |          | 0              |                | 0              | , e                 | DCR r      | 0                | 0              | D     | D     | D     | 1              | 0              | 1              | Decrement register                    |

| LDAX B         0         0         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         1         1         1         1         1         1 <td></td> <td></td> <td></td> <td></td> <td></td> <td><u> </u></td> <td>-</td> <td></td> <td>-</td> <td></td> <td>INR M</td> <td>0</td> <td>0</td> <td>1</td> <td>1</td> <td>0</td> <td>1</td> <td>0</td> <td>0</td> <td>Increment memory</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |            |                  |                |       |                | <u> </u> | -              |                | -              |                     | INR M      | 0                | 0              | 1     | 1     | 0     | 1              | 0              | 0              | Increment memory                      |

| LDAX D         0         0         0         0         0         0         0         0         0         0         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1 <td></td> <td></td> <td></td> <td>-</td> <td></td> <td></td> <td>-</td> <td>· ·</td> <td>-</td> <td></td> <td>DCR M</td> <td>0</td> <td>0</td> <td>1</td> <td>1</td> <td>0</td> <td>1</td> <td>0</td> <td>1</td> <td>Decrement memory</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |            |                  |                | -     |                |          | -              | · ·            | -              |                     | DCR M      | 0                | 0              | 1     | 1     | 0     | 1              | 0              | 1              | Decrement memory                      |

| STA         0         0         1         1         0         0         1         0         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |                  |                | -     |                |          |                |                | -              |                     | INX B      | 0                | 0              | 0     | 0     | 0     | 0              | 1              | 1              |                                       |